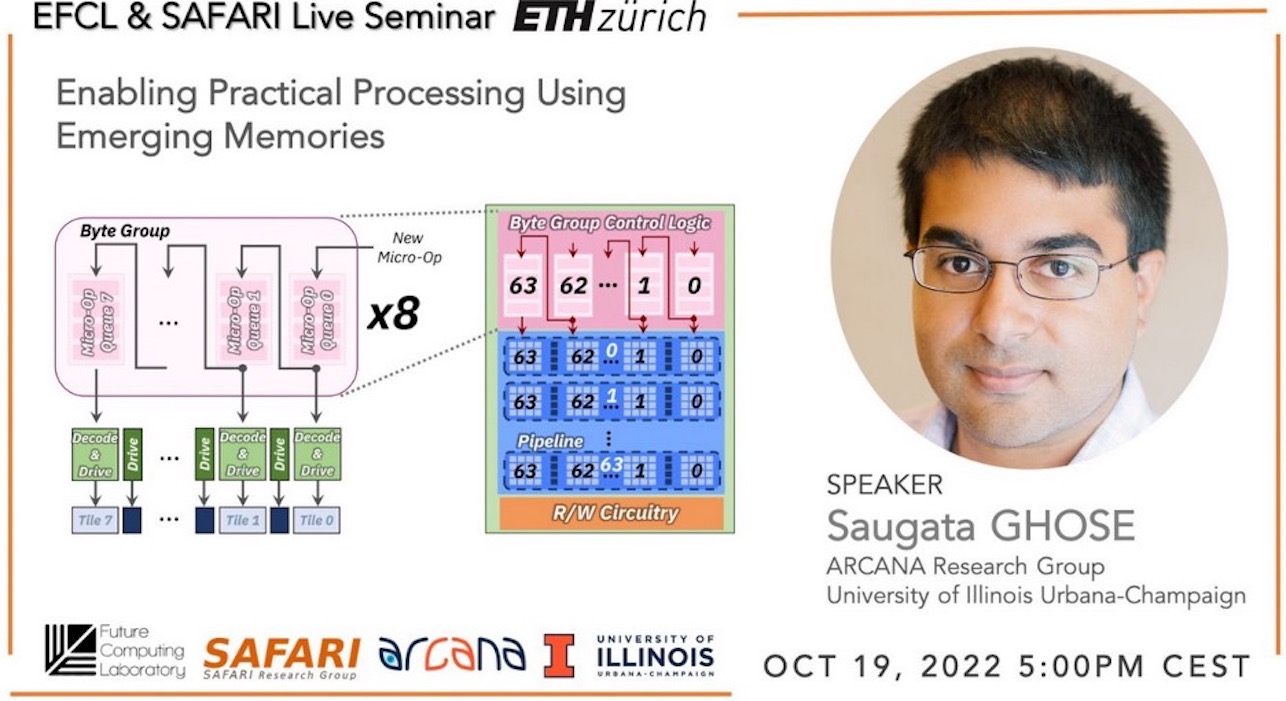

Enabling Practical Processing Using Emerging Memories

Join us for our upcoming Future Computing Seminar Series

Speaker: external page Saugata Ghose, University of Illinois at Urbana-Champaign

Date: October 19th, 2022, 17:00 CET

Where: ETZ J64.1

Abstract:

In recent years, there has been a rapid emergence of data-centric applications that spend a significant fraction of their time on accessing and processing very large datasets. Example applications include precision medicine, computer vision, unmanned vehicles, smart cities, graph frameworks, and mobile device workloads. Unfortunately, contemporary hardware platforms remain compute centric, relying on decades-old design principles. The mismatch between compute-centric architectures and modern data-centric applications results in poor cache utilization, excessive off-chip memory traffic, and significant energy and performance inefficiencies.

In this talk, we discuss our recent efforts on designing practical processing-using-memory (PUM) architectures to overcome this mismatch. We exploit emerging memories to enable a non-von-Neumann architecture that performs computation using direct interactions between memory cells. While there has been significant academic research on the opportunities for PUM architectures provided by emerging memories, these works tend to overlook critical device limitations that prevent their practical commercial deployment. We, instead, take a highly-integrated approach, co-designing device-level innovations to accommodate device non-idealities, circuit-level innovations to amortize control circuit and peripheral overheads, and architecture-level innovations to extract new opportunities for data parallelism and energy efficiency.

Our resulting co-designed PUM architecture, RACER, can unlock 100x+ performance improvements and 180x+ energy savings for data-centric program kernels over a state-of-the-art 16-core CPU, while using practical-to-manufacture resistive memory arrays (e.g., ReRAM, MRAM) and access topologies. We will conclude by discussing future work on innovations across the entire compute stack to realize real commercial PUM systems such as RACER, and how such systems have the potential to become a cornerstone of future edge computing systems.

Speaker Bio:

Saugata Ghose is an assistant professor in the Department of Computer Science at the University of Illinois Urbana-Champaign, where he leads the ARCANA Research Group. He holds M.S. and Ph.D. degrees in electrical and computer engineering from Cornell University, and dual B.S. degrees in computer science and in computer engineering from Binghamton University, State University of New York. Prior to joining Illinois, he was a postdoc and later a systems scientist at Carnegie Mellon University. He received the best paper award from DFRWS-EU in 2017 for work on solid-state drive forensics, and was a 2019 Wimmer Faculty Fellow at CMU. Two of his recent works were named finalists for the NVMW Memorable Paper Award and the Intel Hardware Security Academic Award. His current research interests include data-oriented computer architectures and systems, new interfaces between systems software and hardware, energy-efficient memory and storage, and architectures for emerging platforms and domains. For more information, please visit his website at https://ghose.cs.illinois.edu/